## 4 x 6W POWER AMPLIFIER FOR CAR RADIO

- HIGH POWER CAPABILITY:

4x6W min/4Ω @14.4V, 1KHz, 10%

4x10W typ/2Ω @14.4V, 1KHz, 10%

- MINIMUM EXTERNAL COMPONENT COUNT

- INTERNALLY FIXED GAIN (20dB)

- NO BOOTSTRAP CAPACITORS

- NO EXTERNAL COMPENSATION

- ST-BY FUNCTION (CMOS COMPATIBLE)

- MUTE FUNCTION (CMOS COMPATIBLE)

- NO AUDIBLE POP DURING MUTE/ST-BY OPERATIONS

- LOW SUPPLY SELF MUTING

- PROGRAMMABLE TURN ON DELAY

#### **PROTECTIONS:**

- AC OUTPUT SHORT CIRCUIT TO GND

- DC OUTPUT SHORT CIRCUIT TO GND AND TO V<sub>S</sub> AT POWER ON

- SOFT THERMAL LIMITER

- OVERRATING CHIP TEMPERATURE

- LOAD DUMP VOLTAGE

- FORTUITOUS OPEN GND

- REVERSED BATTERY

- ESD PROTECTION

#### **DESCRIPTION**

The TDA7372A is a new technology class AB quad channels Audio Power Amplifier in Multiwatt15 package designed for car radio applications.

Thanks to the fully complementary PNP/NPN output configuration the TDA7372A delivers a rail to rail voltage swing with no need of boostrap capacitors.

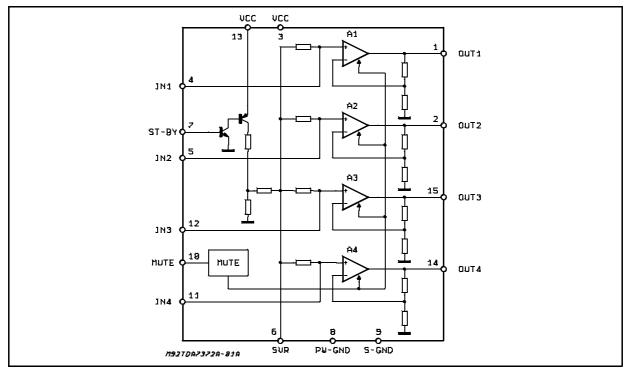

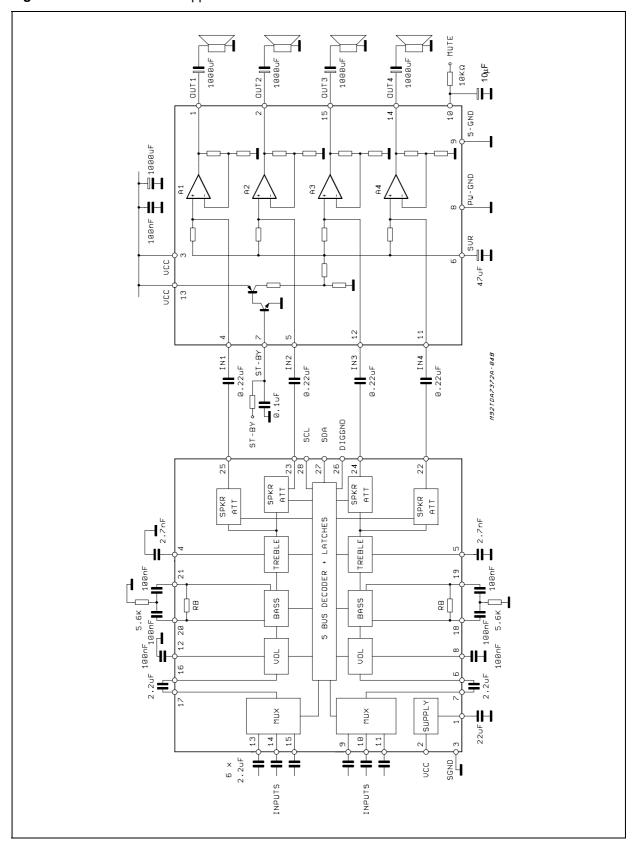

#### **BLOCK DIAGRAM**

September 2003 1/10

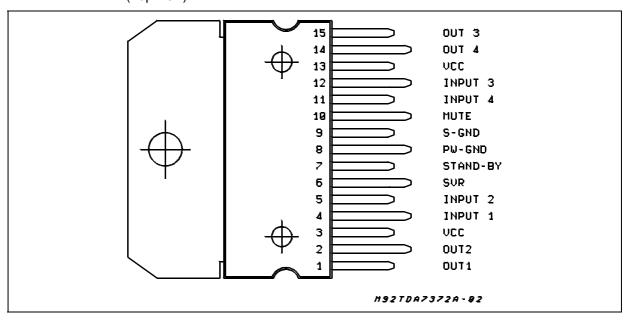

## **PIN CONNECTION** (Top view)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                    | Value      | Unit |

|------------------|----------------------------------------------|------------|------|

| Vs               | DC Supply Voltage                            | 28         | V    |

| $V_{OP}$         | Operating Supply Voltage                     | 18         | V    |

| $V_{PEAK}$       | Peak Supply Voltage (t = 50ms)               | 50         | V    |

| lo               | Output Peak Current (not rep. t = 100μs)     | 4          | Α    |

| lo               | Output Peak Current (rep. f > 10Hz)          | 3          | Α    |

| P <sub>tot</sub> | Power Dissipation (T <sub>case</sub> = 85°C) | 32         | W    |

| $T_{stg}, T_{j}$ | Storage and Junction Temperature             | -40 to 150 | °C   |

#### **THERMAL DATA**

| Symbol                 | Description                      |     | Value | Unit |

|------------------------|----------------------------------|-----|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case | Max | 2     | °C/W |

## **ELECTRICAL CHARACTERISTICS** (Refer to the test circuit; $V_S = 14.4V$ ; $R_L = 4\Omega$ , $T_{amb} = 25^{\circ}C$ , f = 1kHz, unless otherwise specified)

| Symbol              | Parameter                     | Test Condition                                       | Min. | Тур.     | Max. | Unit     |

|---------------------|-------------------------------|------------------------------------------------------|------|----------|------|----------|

| Vs                  | Supply Range                  |                                                      | 8    |          | 18   | V        |

| l <sub>d</sub>      | Total Quiescent Drain Current | Quiescent Drain Current                              |      |          | 150  | mA       |

| Po                  | Output Power                  | $R_L = 4\Omega$ ; THD = 10% each channel             | 6    | 6.5      |      | W        |

|                     |                               | $R_L = 2\Omega$ ; THD = 10% each channel             |      | 10       |      | W        |

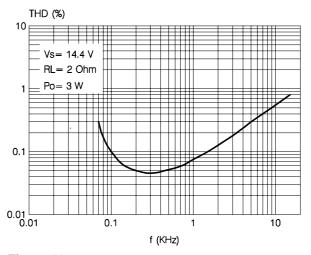

| d                   | Distortion                    | $R_L = 4\Omega;$<br>$P_O = 0.1 \text{ to } 3W$       |      | 0.04     | 0.3  | %        |

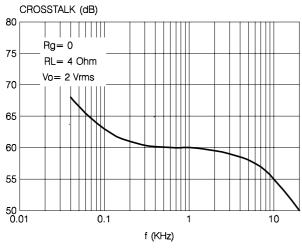

| СТ                  | Cross Talk                    | $f = 1kHz; R_g = 0$<br>$f = 10kHz; R_g = 0$          | 54   | 60<br>55 |      | dB<br>dB |

| R <sub>IN</sub>     | Input Impedance               |                                                      | 35   |          |      | ΚΩ       |

| $G_V$               | Voltage Gain                  |                                                      | 19   | 20       | 21   | dB       |

| $G_V$               | Voltage Gain Match.           |                                                      |      |          | 1    | dB       |

| BW                  | Bandwidth                     | @ -3dB                                               | 100  |          |      | KHz      |

| E <sub>NO</sub>     | Output Noise Voltage (*)      | $R_g = 0$                                            |      |          | 120  | μV       |

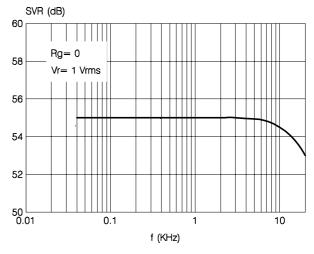

| SVR                 | Supply Voltage Rejection      | $R_g = 0$ ; $f = 100Hz$                              | 48   |          |      | dB       |

| ASB                 | Stand-by Attenuation          |                                                      | 80   |          |      | dB       |

| $I_{SB}$            | ST-BY Current Consumption     | Vpin7 = 1.5V                                         |      |          | 100  | μΑ       |

| I <sub>PIN 7</sub>  | ST-BY Pin Current             | Play mode; Vpin7 = 5V                                |      |          | 30   | μΑ       |

|                     |                               | Output Under Short (Max driving current under fault) |      |          | 5    | mA       |

| $V_{SB\ IN}$        | ST-BY IN Threshold Voltage    |                                                      |      |          | 1.5  | V        |

| V <sub>SB OUT</sub> | ST-BY OUT Threshold Voltage   |                                                      | 3.5  |          |      | V        |

| A <sub>M</sub>      | MUTE Attenuation              |                                                      |      | 80       |      | dB       |

| V <sub>MIN</sub>    | MUTE IN Threshold Voltage     |                                                      |      |          | 1.5  | V        |

| $V_{MOUT}$          | MUTE OUT Threshold Voltage    |                                                      | 3.5  |          |      | V        |

<sup>(\*) 22</sup>Hz to 22KHz

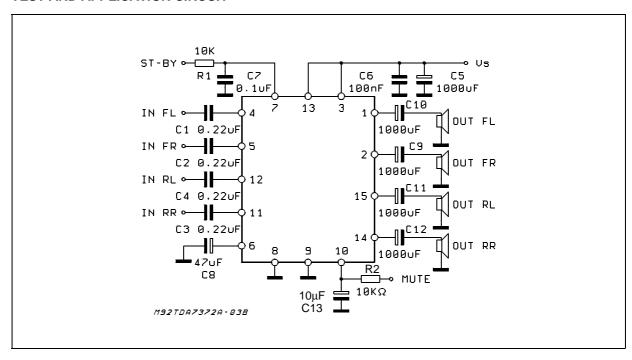

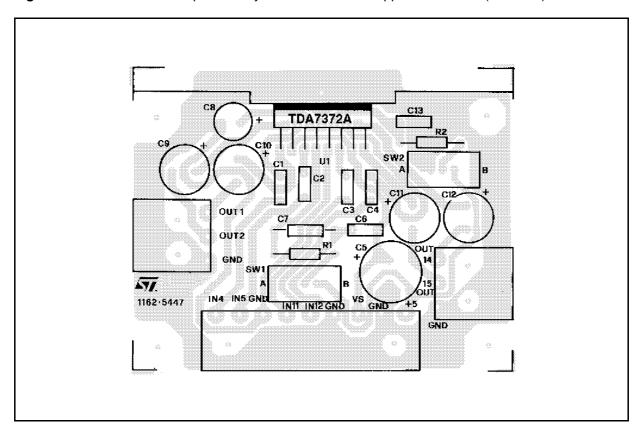

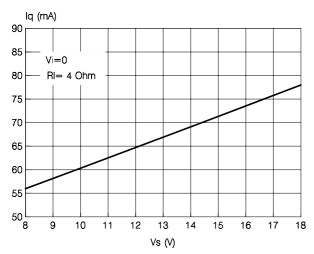

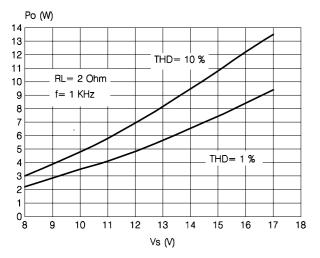

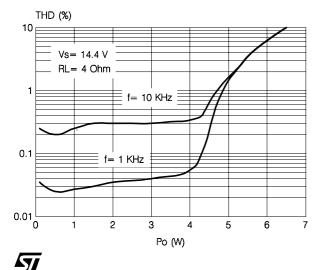

#### **TEST AND APPLICATION CIRCUIT**

Figure 1: P.C. Board and components layout of the Test and Application Circuit (1:1 scale)

Figure 2: Quiescent Drain Current vs. Supply Voltage

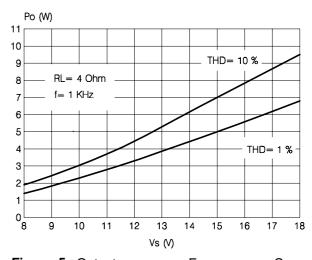

Figure 4: Output Power vs Supply Voltage

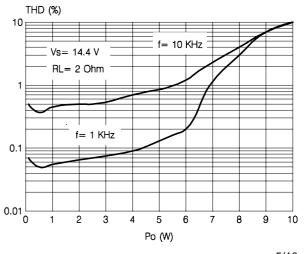

Figure 6: Distortion vs. Output Power

Figure 3: Output Power vs. Supply Voltage

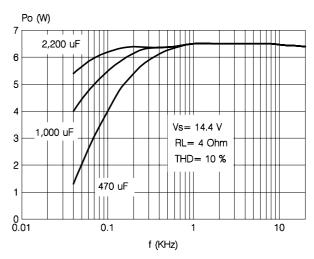

**Figure 5:** Output power vs. Frequency vs.Cout Value

Figure 7: Distortion vs. Output Power

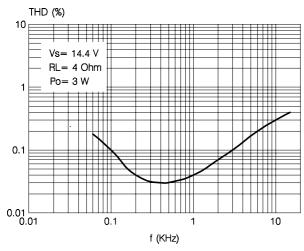

Figure 8: Distortion vs. Frequency

Figure 10: Cross-Talk vs. Frequency

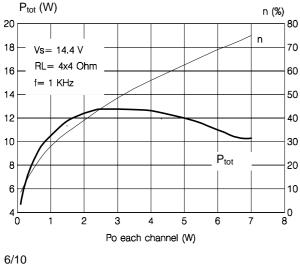

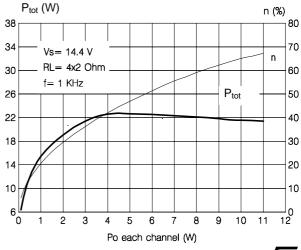

Figure 12: Total Power Dissipation and Efficiency vs. Output Power

Figure 9: Distortion vs. Frequency

Figure 11: Supply Voltage Rejection vs. Frequency

Figure 13: Total Power Dissipation and Efficiency vs. Output Power

Figure 14: TDA7313 + 7372 Application Circuit

### **FUNCTIONAL DESCRIPTION**

| Function                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERAL                                 | The TDA7372A is a quad channel single package audio power amplifier intended to reduce the mismatch in the electrical characteristics among the four different channels and to consistently drop the external component count. It contains four non inverting stages capable to operate down to 20dB gain so minimizing the output noise and optimizing SVR and distortion.                                                                                                                                                                                                                                                                                                                                                                        |

| OUTPUT STAGE                            | The output stage is a single ended type suitable to drive $4\Omega$ loads. It consists of a class AB fully complementary PNP/NPN stages short circuit protected. A rail to rail output swing is achieved without need of boostrap capacitors. Moreover, the external compensation is not necessary.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ST-BY                                   | The device features a St-BY function which shuts down the internal bias generators when the ST-BY input is low. In ST-BY mode the amplifier sinks a small current (in the range of few $\mu$ As). When the St-BY pin is high the IC becomes fully operational.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MUTE                                    | A mute function is also provided. This reduces the gain of the input stage to a level effectively eliminating any audio input influence on the output stage when the mute line is low. When the mute line is high the normal input path is restored. The device goes automatically into mute state when the supply voltage goes below the minimum allowable value. This prevents pop noises whenever the battery voltage drops below a fixed threshold. When the supply voltage rises to it nominal value the device recovers the play condition with a delay fixed by the $C_{\text{SVR}}$ capacitor.                                                                                                                                             |

| THERMAL<br>PROTECTION                   | The Thermal protection principle involves two different steps a) Soft thermal limitation b) Shutdown As long as the junction temperature remains below a preset threshold, the I.C. will deliver the full power. Once the threshold has been reached, the device automatically goes into mute status. The play to mute transition is internally controlled so producing a soft muting without unpleasant effect. Supposing the junction temperature does not reduce to safe levels, a complete shutdown will occur.                                                                                                                                                                                                                                |

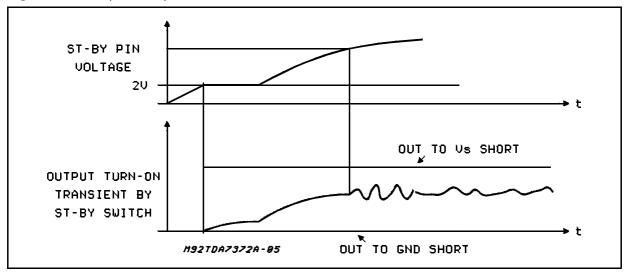

| BUILT-IN SHORT<br>CIRCUIT<br>PROTECTION | A built-in protection circuit assures reliable and safe operation in presence of: - AC short circuit to GND - DC short circuit to GND and to $V_S$ during power-on phase The DC short protector acts in a way to avoid that the device is being turned on (by ST-BY) when a DC short is present from OUT to GND or OUT to $V_S$ . Due to this reason it is necessary to introduce a proper delay on the st-by pin (expecially when it is driven by $V_S$ .) Moreover, as the involved circuitry is normally disabled when a current higher than 5mA is fed into the st-by pin, it is important, in order not to disable it, to have the external current source driving the pin itself limited to 5mA. (figure 1 is shows the relevant waveforms). |

Figure 15: Fault (DC short) waveforms

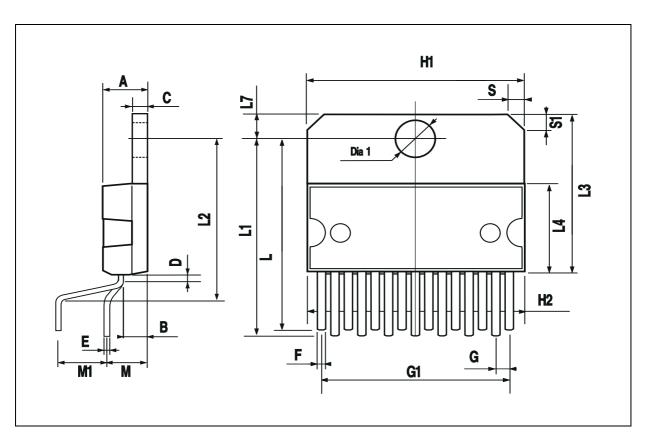

| DIM. |       | mm    |       |       | inch  |       |

|------|-------|-------|-------|-------|-------|-------|

| DIN. | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α    |       |       | 5     |       |       | 0.197 |

| В    |       |       | 2.65  |       |       | 0.104 |

| С    |       |       | 1.6   |       |       | 0.063 |

| D    |       | 1     |       |       | 0.039 |       |

| Е    | 0.49  |       | 0.55  | 0.019 |       | 0.022 |

| F    | 0.66  |       | 0.75  | 0.026 |       | 0.030 |

| G    | 1.02  | 1.27  | 1.52  | 0.040 | 0.050 | 0.060 |

| G1   | 17.53 | 17.78 | 18.03 | 0.690 | 0.700 | 0.710 |

| H1   | 19.6  |       |       | 0.772 |       |       |

| H2   |       |       | 20.2  |       |       | 0.795 |

| L    | 21.9  | 22.2  | 22.5  | 0.862 | 0.874 | 0.886 |

| L1   | 21.7  | 22.1  | 22.5  | 0.854 | 0.870 | 0.886 |

| L2   | 17.65 |       | 18.1  | 0.695 |       | 0.713 |

| L3   | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |

| L4   | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |

| L7   | 2.65  |       | 2.9   | 0.104 |       | 0.114 |

| М    | 4.25  | 4.55  | 4.85  | 0.167 | 0.179 | 0.191 |

| M1   | 4.63  | 5.08  | 5.53  | 0.182 | 0.200 | 0.218 |

| S    | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| S1   | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| Dia1 | 3.65  |       | 3.85  | 0.144 |       | 0.152 |

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2003 STMicroelectronics - All rights reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia – Belgium - Brazil - Canada - China – Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com

4